要闻:在ADSP-BF561上实现与优化的H.264

【资料图】

【资料图】

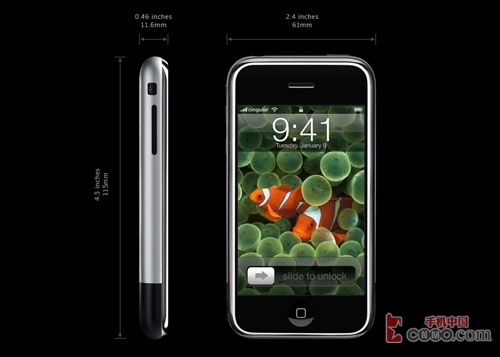

目前,音视频技术日新月异,其中,视频实时编码传输极具代表性。在视频压缩算法领域,新一代视频压缩标准H.264以其优异的压缩性能和图像质量使视频实时编码传输技术的实现成为可能。但该标准的计算复杂度高,用一般的图像处理芯片难以达到实时编解码的要求,它需要快速、稳定的处理器作为硬件平台。ADSP-BF561是ADI公司推出的高性能多媒体处理器。其主要特点是具有两个ADSP-BF533处理器核心(以下简称核心A和核心B),最高时钟频率达到600MHz,其内部采用哈佛总线结构,存储模型层次化。其典型应用模式是A核运行嵌入式操作系统,B核运行多媒体处理算法,如H.264。本文提出了一套采用ADSP-BF561芯片实现H.264视频压缩算法的设计方案,结合该DSP平台对算法进行了针对性的优化,充分发挥了ADSP-BF561强大的处理能力。

1 算法介绍

1.1 H.264编码模型框架

H.264以其高压缩比、高图像质量和良好的网络亲和性广受业界欢迎。在同等质量条件下,H.264的数据压缩比比MPEG-2高2~3倍,比MPEG-4高1.5~2倍。其需要的带宽只有MPEG-4的50%, MPEG-2的12.5%。

H.264标准采用分层体系结构,系统分为:视频编码层VCL(Video CodingLayer),负责高效的数字视频压缩;网络抽象层NAL(Network AbstractionLayer),负责对数据进行打包和传送。H.264编码图像通常分为三种类型:I帧、P帧、B帧。I帧为帧内编码帧,其编码不依赖于已编码的图像数据。P帧为前向预测帧,B帧为双向预测帧,编码时都需要根据参考帧进行运动估计。同时,H.264在提高图像传输容错性方面做了大量工作,重新定义了适于图像的结构划分。在编码时,图像帧各部分被划分到多个Slice结构中,每个Slice都可以被独立编码,不受其他部分影响。Slice由图像最基本的结构——宏块组成,每个宏块包含一个16×16的亮度块和两个8×8的色度块。H.264标准的整体编码框图如图1所示。编码过程中,原始数据进入编码器后,当采用帧内编码时,首先选择相应的帧内预测模式进行帧内预测,随后对实际值和预测值之间的差值进行变换、量化和嫡编码,同时编码后的码流经过反量化和反变换之后重构预测残差图像,再与预测值相加得出重构帧,得出的结果经过去块滤波器平滑后送入帧存储器。采用帧间编码时,输入的图像块首先在参考帧中进行运动估计,得到运动矢量。运动估计后的残差图像经整数变换、量化和嫡编码后与运动矢量一起送入信道传输。同时另一路码流以相同的方式重构后,经去块滤波后送入帧存储器作为下一帧编码的参考图像。

1.2 H.264关键技术

1.2.1 帧内预测

H.264引入了帧内预测以提高压缩效率。帧内预测编码就是利用周围邻近的像素值来预测当前的像素值,然后对预测误差进行编码。这种预测是基于块的。对于亮度分量,块的大小可以在16×16和4×4之间选择,16×16有4种预测模式,4×4有9种预测模式;对于色度分量,预测是对整个8×8块进行的,有4种预测模式。

1.2.2 帧间预测

帧间预测时所用块的大小可变。假设基于块的运动模型,其块内的所有像素都做了相同的平移,在运动比较剧烈或者运动物体的边缘外,这一假设会与实际出入较大,从而导致较大的预测误差,这时减小块的大小可以使假设在小块中依然成立。另外小块所造成的块效应相对也小,因此,小块可以提高预测的效果。H.264一共采用了7种方式对一个宏块进行分割,每种方式下块的大小和形状都不相同,编码器可以根据图像的内容选择最好的预测模式。与仅使用16x16块进行预测相比,使用不同大小和形状的块可以使码率节约15%以上。

同时,帧内预测采用了更精细的预测精度,H.264中亮度分量的运动矢量使用1/4像素精度。色度分量的运动矢量使用1/8像素精度。

1.2.3 多帧参考

H.264支持多帧参考预测,最多可以有5个在当前帧之前的解码帧作为参考帧产生对当前帧的预测,提高H.264解码器的错误恢复能力。

1.2.4 整数变换

H.264对残差图像的4×4整数变换技术,采用定点运算来代替以往DCT变换中的浮点运算。以降低编码时间,同时也更适合硬件平台的移植。

1.2.5 熵编码

H.264支持两种熵编码方法,即CAVLC(基于上下文的自适应可变长编码)和CABAC(基于上下文的自适应算术编码)。其中CAVLC的抗差错能力比较高,但编码效率比CABAC低;而CABAC的编码效率强,但需要的计算量和存储容量更大。

1.2.6 去方块滤波

去方块滤波的作用是消除经反量化和反变换后重建图像中由于预测误差产生的块效应,从而改善图像的主观质量和预测误差。经过滤波后的图像将根据需要放在缓存中用于帧间预测,而不是仅仅用来改善主观质量,因此该滤波器位于解码环中。对于帧内预测,使用的是未经过滤波的重建图像。

2 算法实现

2.1 平台选择

2.1.1 ADSP-BF561芯片介绍

ADSP-BF561是Blackfin系列中的一款高性能定点DSP视频处理芯片。其主频最高可达750MHz,内核包含2个16位乘法器MAC、2个40位累加器ALU、4个8位视频ALU,以及1个40位移位器。该芯片中的两套数据地址产生器(DAG)可为同时从存储器存取双操作数提供地址,每秒可处理1 200兆次乘加运算。芯片带有专用的视频信号处理指令以及100KB的片内L1存储器(16KB的指令Cache,16 KB的指令SRAM,64 KB的数据Cache/SRAM,4 KB的临时数据SRAM)、128KB的片内L2存储器SRAM,同时具有动态电源管理功能。此外,Blackfin处理器还包括丰富的外设接口,包括EBIU接口(4个128 MBSDRAM接口,4个1MB异步存储器接口)、3个定时/计数器、1个UART、1个SPI接口、2个同步串行接口和1路并行外设接口(支持ITU-656数据格式)等。Blackfin处理器在结构上充分体现了对媒体应用(特别是视频应用)算法的支持。

2.1.2 ADSP-561 EZkite

ADSP-BF561视频编码器平台采用ADI公司的ADSP-BF561 EZ-kitLite评估板。此评估板包括1块ADSP-BF561处理器、32 MB SDRAM和4 MBFlash,板中的AD-V1836音频编解码器可外接4输入/6输出音频接口;而ADV7183视频解码器和ADV7171视频编码器则可外接3输入/3输出视频接口。此外,该评估板还包括1个UART接口、1个USB调试接口和1个JTAG调试接口。摄像头输入的模拟视频信号经视频芯片ADV7183A转化为数字信号,此信号从ADSP-BF561的PPI1(并行外部接口)进入ADSP-BF561芯片进行压缩,压缩后的码流则经ADV7179转换后从ADSP-BF561的PPI2口输出。此系统可通过Flash加载程序,并支持串口及网络传输。编码过程中的原始图像、参考帧等数据可存储在SDRAM中。

2.2 算法选取与优化方案

2.2.1 算法选取

H.264实现的源代码不止一种,其中最常见的有JM、X264和T264。对比这三种实现源代码,X264比T264具有更高的效率。而且相比广泛采用的JM编码模型,X264在兼顾编码质量的同时大幅度地提升了编码速度,所以选取X264作为算法原型。

2.2.2 优化方案

该优化方案从三个层次对算法进行优化:算法层次、代码层次、平台层次。下面介绍具体优化方法。

2.2.2.1 编码器具体参数的选择

该编码器使用main档次,I、B、P帧量化值分别为26、31、29,流控参数选为CBR。IDR帧间隔设为50,B帧间隔为2帧。这样的选择是为了在速度和运算量上取折中。选用B帧并将其量化值加大,可比baseline档次、IPPP结构提高约10%的压缩率。而B帧的计算量,因其不用做参考帧,故无需进行去块滤波和插值计算,在31的qp下,很多块会被判做skip模式编码,因而多数时B帧总运算量候反而较P帧低。

2.2.2.2 算法层次的优化

算法层次的优化主要是指在参数选定的情况下,对部分算法所作的替换或优化。和参数的选择一样,算法层次优化也主要受优化策略的指导。如运动匹配准则是选用SSD、SAD或SATD。如果只看中准确程度,则选择SSD最佳;如果只看中运行速度,则选择SAD最佳;如果要兼顾二者,则选用SATD是比较好的一个方案。在进行算法优化时还应该注意一个问题,即要考虑实际运行平台的支持情况。如在追求速度的策略下,匹配准则选用SAD,如果只计算一半的点则会大大降低运算速度。但是如果考虑ADSP-BF561汇编指令的设计情况,就会发现这样做反而会增加指令数,会使速度更低。算法层次优化包括如下几个部分:

(1)除法求余。改进策略是浮点型算法尽量改为整型,64位尽量改为32位,32位尽量改为16位。而对于某些计算比较多的,则改为查表计算。在ADSP-BF561平台上,一次32位整形除法需耗时300个CYCLE,而查表仅需几个CYCLE,这样的改进能显著提高速度。

(2)饱和函数。在视频的计算中,几乎每次像素的计算都会调用饱和函数,X264代码的实现中已将这部分代码改为查表函数,在其他的编解码器实现中也有将这部分改为一个判断和几个逻辑运算的形式。对大部分DSP平台,采用判断跳转会打断流水线,即使平台有比较好的跳转预测功能,打断流水仍然会造成stall。所以查表方法是一种高效方法。而在ADSP-BF561汇编指令中,可以通过设置指令后缀或使用某些特殊指令来进行饱和工作。甚至不用查表,在不同的场合使用不同的饱和算法能大大提高代码的执行效率。

(3)MC部分函数。实测中发现MC部分函数运行效率不如ffmpeg解码器中MC部分效率高,所以将这部分代码用ffmpeg中的相应部分替换。此外qpel16_hv函数中计算有冗余,减少这些冗余能提高代码运行效率。

(4)算法替代和改进。帧间预测的改进:关于算法的改进主要集中在对me(motionestimation)的改进上,流程如图2所示。costmin1=min(cost16,cost8,cost16×8,cost8×16),costmin2=min(costmin1,costsub),依次在16×16、8×8、16×8和8×16大小宏块的整像素位置做预测,再做次像素估计和帧内预测,选用匹配准则函数(采用sad作为匹配准则函数)取得最小值的模式进行编码。每计算一种模式,都将sad值与一个经验阀值做比较。当sad值小于这个阀值时,立即结束运动估计,从而减少运算量。

帧内预测的改进:H.264标准所采用的帧内预测模式除了DC模式都具有方向性,相邻4×4块都具有相关性。根据这样的相关性,只将当前4×4块上边和左边选用预测模式及其相邻的两种预测模式作为当前4×4块的预测模式,当其阀值都大于一个经验阀值时,才采用DC模式。这样的方案不用一一计算9种预测模式,在复杂度、编码效率、质量和速度上取了一个折中。流程如图3所示。

2.2.2.3 代码层次优化

针对ADSP-BF561平台,代码层次的优化工作包括以下几个方面:

(1)内联函数。将经常调用的函数体较小的函数改为内联。编译条件中有关于内联函数优化的选项。内联函数的使用是将代码的大小和运行效率取一个折中。根据实际情况,代码的大小并非限制条件,所以应尽可能多地使用内联函数。在项目配置中选中when declared inline选项。

(2)跳转预测。ADSP-BF561采用了静态预测的方式来预测有条件判断情况,预测不成功会造成4~8个内核时钟(CCLK)的延误。如果事先知道某些跳转的概率,将可能性最大的分支放在最前面,可以从概率上降低预测不成功而造成的stall。

(3)使用硬件支持循环。对于大部分平台,将一些循环体小的循环展开也能提高效率。ADSP-BF561有两组硬件计数器用以支持循环。所以除非是展开三层以上的循环,否则,展开循环体不能提高效率。

(4)内存。嵌入式系统的内存是非常宝贵的资源。避免频繁的动态申请和释放内存,能减少碎片产生,提高内存的利用率。X264工程也不会频繁地申请释放内存。在项目中,具体做法是编写平台相关的malloc和free函数。将经常使用的中间数据在L1数据空间中分配。

(5)注释不需要代码。去掉代码中不需要的部分,主要会去掉CAVLC以及部分码率控制、csp、cpu、信息统计、调试和psnr计算等部分代码,这样做的目的是为了减小文件大小和去除代码中的一些跳转。不建议删除代码,可以使用注释符或用宏切换的方式,以防止以后参数改变时需要使用未使用过的代码。

2.2.2.4 平台层次优化

ADSP-BF561相应的编程参考和硬件参考对其平台特性有详细介绍。一些平台自带的优化功能,如CACHE的开启和配置等不专门在此讨论。

- 环球新消息丨小米4C和小米4i哪个好 小米4C与4i的区别对比评测详解

- 微资讯!diy是什么意思-电脑diy组装教程

- 全球播报:微信界面怎么设置皮肤

- 全球热议:技嘉主板常见问题与解答

- 今热点:如何安装AppSync补丁 两种完美方法安装AppSync补丁

- 长征七号A运载火箭成功发射中星1E卫星 实现连续三次发射成功

- 环球关注:国产加密手机为何这么火?国产加密手机火爆原因分析

- 天天热讯:qq群怎么匿名聊天

- 看热讯:OPPO FindX2和华为p40哪个好?为一块超感屏唱征服

- 热点评!如何使用百度网盘解析种子

- 魅族PANDAER发布白金星舟耳机与音箱新品 续航更长可降噪

- 环球快资讯:华为mate9什么时候出 华为mate9配置以及价格介绍

- 【环球聚看点】魅族X8和魅族16X哪个值得买 魅族16X和8X区别对比

- 提前激活iPhone14每台罚款20万:新机采用“灵动岛”挖孔设计

- 当前视讯!富士mini25怎么用 富士mini25使用技巧介绍

- 每日热点:小米红米1S手机做工怎么样 红米1S电信版拆机图评测

- 中国6最多、最顺利号码!15666666666靓号拍卖 已有10131次围观

- 【全球速看料】中国移动、联通、电信的4G套餐哪家最划算?

- 育碧公开舞力全开2023版游戏 XboxOne等版本预计11月上线

- Apple Watch Ultra电池容量揭晓:开启低功耗模式后可达到60小时

- 提前激活每台罚款20万!iPhone 14 Pro包装盒提前看:没有塑封包装

- 中国功夫游戏《师父》官宣11月9日登陆NS!直面会后开放预约

- Intel展示80Gbps的雷电新接口 每个通道40Gbps

- 三星全面推广SmartThings 并官宣旗下家电等保修期进一步延长

- 集邦咨询:预测三季度笔电面板出货将环减一成多 仅4510万片

- 东风风行S60EV已通过申报 前脸较前代有大幅变化设计更现代

- 摩托罗拉Edge30Ultra登陆印度市场 主摄为200MP规格支持快充

- 大立光披露最新财务数据:上月营收环增14% 增幅略高于预期

- 神舟十四号乘组在太空吃月饼度中秋:与月亮和嫦娥触手可及

- 大疆最新款运动相机将到来 磁吸拓展形式更加丰富拍摄更便捷

- 全球今热点:贝佐斯的火箭发射失败 但意外验证了逃逸系统

- 焦点速讯:前方高能!索尼SOP一次性展示10款大作

- 环球热门:iPhone14换电池贵了200!容量和13一样但是涨价

- 【世界时快讯】苹果:iOS不能回滚 但是安全补丁可以!

- 最新消息:全新3A大作!EA和光荣联合开发狩猎游戏

- 每日快报!更接近人类驾驶,特斯拉FSD来到临界点?

- 热点在线丨野炊2《塞尔达传说 王国之泪》正式定档,《双人成行》登陆NS

- 天天快资讯:仅需799元 智米纯净加湿器雨林上线众筹

- 环球看点!无感佩戴,耳机的难题它都解决了:索尼开放式真无线耳机LinkBuds

- 环球看热讯:英特尔院士Tom Petersen:持续耕耘游戏优化 确保优质用户体验

- 每日看点!OPPO Watch 3 Pro体验报告:以旗舰特性,开启腕上智慧生活

- 每日快看:豪威推出用于笔记本电脑的HDR 4K摄像头模块OV08X

- 每日关注!苹果iOS 16系统正式版发布:有锁屏个性化和自定义等功能

- 【速看料】抖音921好物节氛围正浓!品牌商家达人乘势增长喜迎开门红

- 今日讯!以电力成就算力 施耐德电气以数字配电方案助力华云数据湖电力运维高效进阶

- 环球快看点丨开辟清洁能源新赛道四季沐歌勇扛“空气源热泵”大旗

- 【当前热闻】超宽、融合、智能、开放,新华三提出云智原生数据中心网络建设思路

- 热议:倍思Ga5Pro氮化镓多功能桌面快充充电器:充电和接口扩展一个搞掂

- 当前报道:宝妈宝爸该用什么枕头?米家智能枕体验,支持睡眠分析与智能联动

- 世界今热点:苹果98元挂绳卖断货/贝佐斯火箭发射失败/新手爸爸大脑会“萎缩”

- 环球新资讯:3DEXPERIENCE线上云平台支持离线工作?是真的!

- 环球精选!对标Redmi!realme Watch 3 Pro发布

- 苹果新机完成3C认证 信息显示其可支持29W快充并兼容多个协议

- iPhone14系列部分订单已显示准备发货 原定发售日为本周五

- 华硕PN52迷你主机全新亮相 16GB内存成标配 售价最高超五千

- 最新款高端苹果手机4K ProRes确定所需存储空间:至少256G

- YOGAPro14s新BIOS接受官方测试:处理器大小核可自定义调整

- 报道称谷歌将为高端ChromeOS产品添加更多更优质的视频效果

- 全球聚焦:在考虑入手三星Fold4的朋友,来看看我的真实用机感受

- 【聚看点】三维菁彩声 为央视秋晚增添8K视听科技亮点

- 全球热文:【新机】又一款套娃机发布,5000mAh+67W快充

- 环球快看:一台12999元的折叠屏手机,买它的人到底有多大的底气?

- 动画电影机器人总动员将发布4K超清蓝光碟 封面将获得特别设计

- 苹果14Pro/Max版本将支持双频GPS定位 所在位置可更加精确

- 【世界播资讯】iPhone11怎么连接电脑?iPhone11信任并连接电脑图文教程

- 焦点关注:飞机上拍到神仙?网友拍到云上站着人,还自带佛光

- 环球关注:iPhone 14系列新机真的香,搭配闪魔配件使用更佳

- 全球热推荐:为什么这么薄?拆解欣博阅G6

- 世界观察:华为nova3i怎么样 华为Nova3i配置参数、价格及真机图赏

- 当前看点!超链接去掉下划线方法

- 每日短讯:荣耀4C有几个版本?华为荣耀4C畅玩版各版本区别介绍

- 每日快播:夏天防晒科普:SPF指数是什么? 防晒霜防晒指数

- 电子纸厂商元太八月营收约环增一成多 同增翻倍再创单月新高

- 环球时讯:七子白到底是什么白? 七子白中药面膜配方

- 报道:魅族Pro6 Plus做工怎么样?魅族Pro6 Plus拆机全过程图解

- 【天天播资讯】电脑提示宽带连接错误734如何解决

- 全球热推荐:造孩子的正确姿势是怎样的?如何造 怎么造

- 今日观点!小米Max2和小米max有什么区别?小米Max2和小米max区别对比详细评测

- 天天微速讯:马拉松的由来 马拉松原指什么

- 速读:小米10t对比小米10哪个比较好?

- 全球微速讯:怎么关闭qq空间

- 头条焦点:LG G6和LG V20哪个值得买?LG G6和LG V20区别对比评测

- 【世界速看料】苹果手机如何录音?如何使用苹果录音功能?

- 每日看点!win7配置最低要求是什么? windows7 配置要求?

- 快报:Win7系统提示windows主进程rundll32已停止工作怎么办

- 全球最资讯丨中流击楫是谁的故事

- 世界报道:阿里旅行去啊信用住的使用方法

- 热推荐:未能恢复iphone发生未知错误3194怎么办

- 焦点快看:华为5G首席科学家—带你了解5G网络标准是如何建立的

- 全球热文:三星向芯片厂罹癌员工道歉并承诺补偿

- 全球看热讯:苹果手机怎么分屏?iPhone应用分屏教程

- LG开售万元超宽屏双QHD显示器 配置可调节底座还能反向供电

- 【当前独家】哈尔滨乔四黑社会集团 中国黑社会老大乔四

- 天天新资讯:我们经常饲养的宠物龙猫是猫吗-宠物龙猫是猫吗

- 世界快消息!如何退订火车票 火车票网上订票退票

- 环球动态:iphone铃声目录在哪自定义iphone手机铃声

- 天天关注:碳化硅(SiC)功率器件或在电动汽车领域一决胜负

- 环球观速讯丨原道N70双擎S玩家拆机

- 环球微资讯!Apple香港官网放货啦 原价购买港版iPhone 6/6Plus攻略

- 全球通讯!iOS 9正式版下载地址(iPhone/iPad/iTouch) 附升级教程!

新闻排行

精彩推荐

- 【世界时快讯】苹果:iOS不能回滚 但是安全补丁可以!

- 焦点速讯:前方高能!索尼SOP一次性展示10款大作

- 最新消息:全新3A大作!EA和光荣联合开发狩猎游戏

- 全球今热点:贝佐斯的火箭发射失败 但意外验证了逃逸系统

- 环球热门:iPhone14换电池贵了200!容量和13一样但是涨价

- 热点在线丨野炊2《塞尔达传说 王国之泪》正式定档,《双人成行》登陆NS

- 天天快资讯:仅需799元 智米纯净加湿器雨林上线众筹

- 【当前热闻】超宽、融合、智能、开放,新华三提出云智原生数据中心网络建设思路

- 热议:倍思Ga5Pro氮化镓多功能桌面快充充电器:充电和接口扩展一个搞掂

- 今日讯!以电力成就算力 施耐德电气以数字配电方案助力华云数据湖电力运维高效进阶

超前放送

- 焦点速递!HTC U11和三星S8哪个...

- 全球热文:初学者买什么吉他 具...

- 天天快看:三星手机移动数据连接...

- 今日讯!2020国内奶粉排名前十名...

- 最资讯丨风暴播放器调出播放进度...

- 世界观焦点:小年夜是指哪一天几...

- 每日头条!蚂蚁庄园6月20日答案最...

- 世界看点:iphone怎么添加厦门公...

- 全球观点:一差半错是什么意思 ...

- 环球动态:鬼谷子下山的故事 鬼...

- 世界讯息:支付宝扫福字2022什么...

- 全球即时:Corel VideoStudio ...

- 天天信息:icloud存储满了怎么办...

- 天天快报!怎样水养富贵竹 水养...

- 【独家焦点】千元以下智能手机有...

- 要闻:在ADSP-BF561上实现与优化的H.264

- 新消息丨ota是什么?ota升级是什...

- 全球观热点:fps不稳定怎么办

- 全球最资讯丨手写电脑多少钱 手...

- 【播资讯】三星W2016手机怎么样...

- 世界快资讯:acer笔记本电脑怎么样

- 环球新消息丨先科热水器怎么样 ...

- 世界速看:mds文件用什么打开

- 天天微速讯:怎样进入dos?进入d...

- 焦点播报:空调一小时几度电

- 当前时讯:傍组词语 汉字傍组词语

- 环球视讯!iPhoneSE2屏幕分辨率是多少?

- 环球微动态丨梨花烫最新款短发 ...

- 当前关注:10万元左右的车哪款好...

- 全球热门:ireader(爱读掌阅)安卓...

- 世界焦点!红魔3手机值不值得买...

- 当前快报:大漠孤火烟直长河落日...

- 玉兔二号月球车已登陆月背工作三...

- 天天新动态:一加9和一加9pro区...

- 世界快讯:清平乐·金风细细——...

- 天天时讯:iPhone12系列电池容量...

- 环球速看:windows bat(批处理):IF详解

- 世界头条:华为手机怎么连接电脑...

- 播报:诺基亚603多少钱 诺基亚6...

- 当前头条:如何维修德龙咖啡机 ...

- 世界今日讯!iphone x怎么设置l...

- 环球信息:软件测试工作流程图

- 全球滚动:苏州有什么好玩的地方...

- 天天快资讯丨山西洪洞县大槐树老...

- 全球最资讯丨便携式冰箱怎么样?...

- 当前热点-360浏览器好不好用

- 天天快看点丨iphone13多少钱 苹...

- 观焦点:苹果手机怎么定位 苹果...

- 观察:QQ等级计算规则(最新版)

- 前沿热点:乐蜂网app下载安装 ...