全球观焦点:DSP入门知识

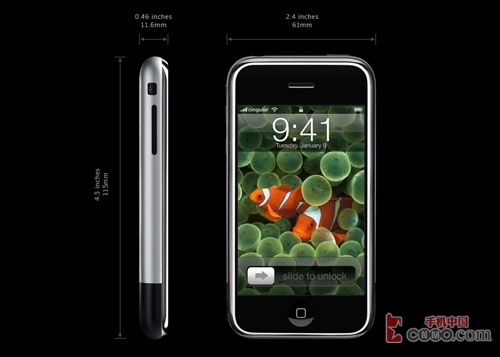

(资料图片仅供参考)

(资料图片仅供参考)

Digital Signal Processing 数字信号处理

作为一个案例研究,我们来考虑数字领域里最通常的功能:滤波。简单地说,滤波就是对信

号进行处理,以改善其特性。例如,滤波可以从信号里清除噪声或静电干扰,从而改善其信

噪比。为什么要用微处理器,而不是模拟器件来对信号做滤波呢?我们来看看其优越性:

模拟滤波器(或者更一般地说,模拟电路)的性能要取决于温度等环境因素。而数字滤波器

则基本上不受环境的影响。

数字滤波易于在非常小的宽容度内进行复制,因为其性能并不取决于性能已偏离正常值的器

件的组合。

一个模拟滤波器一旦制造出来,其特性(例如通带频率范围)是不容易改变的。使用微处理

器来实现数字滤波器,就可以通过对其重新编程来改变滤波的特性。

信号处理方式的比较

比较因素 模拟方式 数字方式

修改设计的灵活性 修改硬件设计,或调整硬件参数 改变软件设置

精度 元器件精度 A/D 的位数和计算机字长,算法

可靠性和可重复性 受环境温度、湿度、噪声、 不受这些因素的影响

电磁场等的干扰和影响大

大规模集成 尽管已有一些模拟集成电路, 但品种较少、集成度不高、价格较高DSP 器件

体积小、功能强、功耗小、一致性好、使用方便、性能/价格比高

实时性 除开电路引入的延时外,处理是实时的 由计算机的处理速度决定

高频信号的处理 可以处理包括微波毫米波乃至光波信号 按照奈准则的要求,受S/H、A/D

和 处理速度的限制

Digital Signal Processor 数字信号处理器

微处理器(Microprocessor)的分类

通用处理器(GPP)

采用冯.诺依曼结构,程序和数据的存储空间合二而一

8-bit Apple(6502),NEC PC-8000(Z80)

8086/286/386/486/Pentium/Pentium II/ Pentium III

PowerPc 64-bit CPU(SUN Sparc,DEC Alpha, HP)

CISC 复杂指令计算机, RISC 精简指令计算机

采取各种方法提高计算速度,提高时钟频率,高速总线,多级Cashe,协处理器等

Single Chip Computer/ Micro Controller Unit(MCU)

除开通用CPU 所具有的ALU 和CU,还有存储器(RAM/ROM)寄存器,时钟,计数器,

定时器,串/并口,有的还有A/D,D/A

INTEL MCS/48/51/96(98)

MOTOROLA HCS05/011

DSP

采用哈佛结构,程序和数据分开存储

采用一系列措施保证数字信号的处理速度,如对FFT 的专门优化

MCU 与DSP 的简单比较

MCU DSP

低档 高档 低档 高档

指令周期(ns) 600 40 50 5

乘加时间(ns) 1900 80 50 5

US$/MIPS 1.5 0.5 0.15 0.1

DSP 处理器与通用处理器的比较

考虑一个数字信号处理的实例,比如有限冲击响应滤波器(FIR)。用数学语言来说,FIR 滤

波器是做一系列的点积。取一个输入量和一个序数向量,在系数和输入样本的滑动窗口间作

乘法,然后将所有的乘积加起来,形成一个输出样本。

类似的运算在数字信号处理过程中大量地重复发生,使得为此设计的器件必须提供专门的支

持,促成了了DSP 器件与通用处理器(GPP)的分流:

1 对密集的乘法运算的支持

GPP 不是设计来做密集乘法任务的,即使是一些现代的GPP,也要求多个指令周期来做一

次乘法。而DSP 处理器使用专门的硬件来实现单周期乘法。DSP 处理器还增加了累加器寄

存器来处理多个乘积的和。累加器寄存器通常比其他寄存器宽,增加称为结果bits 的额外

bits 来避免溢出。

同时,为了充分体现专门的乘法-累加硬件的好处,几乎所有的DSP 的指令集都包含有显式

的MAC 指令。

2 存储器结构

传统上,GPP 使用冯.诺依曼存储器结构。这种结构中,只有一个存储器空间通过一组总线

(一个地址总线和一个数据总线)连接到处理器核。通常,做一次乘法会发生4 次存储器访

问,用掉至少四个指令周期。

大多数DSP 采用了哈佛结构,将存储器空间划分成两个,分别存储程序和数据。它们有两

组总线连接到处理器核,允许同时对它们进行访问。这种安排将处理器存贮器的带宽加倍,

更重要的是同时为处理器核提供数据与指令。在这种布局下,DSP 得以实现单周期的MAC

指令。

还有一个问题,即现在典型的高性能GPP 实际上已包含两个片内高速缓存,一个是数据,

一个是指令,它们直接连接到处理器核,以加快运行时的访问速度。从物理上说,这种片内

的双存储器和总线的结构几乎与哈佛结构的一样了。然而从逻辑上说,两者还是有重要的区

别。

GPP 使用控制逻辑来决定哪些数据和指令字存储在片内的高速缓存里,其程序员并不加以

指定(也可能根本不知道)。与此相反,DSP 使用多个片内存储器和多组总线来保证每个指

令周期内存储器的多次访问。在使用DSP 时,程序员要明确地控制哪些数据和指令要存储

在片内存储器中。程序员在写程序时,必须保证处理器能够有效地使用其双总线。

此外,DSP 处理器几乎都不具备数据高速缓存。这是因为DSP 的典型数据是数据流。也就

是说,DSP 处理器对每个数据样本做计算后,就丢弃了,几乎不再重复使用。

3 零开销循环

如果了解到DSP 算法的一个共同的特点,即大多数的处理时间是花在执行较小的循环上,

也就容易理解,为什么大多数的DSP 都有专门的硬件,用于零开销循环。所谓零开销循环

是指处理器在执行循环时,不用花时间去检查循环计数器的值、条件转移到循环的顶部、将

循环计数器减1。

与此相反,GPP 的循环使用软件来实现。某些高性能的GPP 使用转移预报硬件,几乎达到

与硬件支持的零开销循环同样的效果。

4 定点计算

大多数DSP 使用定点计算,而不是使用浮点。虽然DSP 的应用必须十分注意数字的精确,

用浮点来做应该容易的多,但是对DSP 来说,廉价也是非常重要的。定点机器比起相应的

浮点机器来要便宜(而且更快)。为了不使用浮点机器而又保证数字的准确,DSP 处理器在

指令集和硬件方面都支持饱和计算、舍入和移位。

5 专门的寻址方式

DSP 处理器往往都支持专门的寻址模式,它们对通常的信号处理操作和算法是很有用的。

例如,模块(循环)寻址(对实现数字滤波器延时线很有用)、位倒序寻址(对FFT 很有用)。

这些非常专门的寻址模式在GPP 中是不常使用的,只有用软件来实现。

6 执行时间的预测

大多数的DSP 应用(如蜂窝电话和调制解调器)都是严格的实时应用,所有的处理必须在

指定的时间内完成。这就要求程序员准确地确定每个样本需要多少处理时间,或者,至少要

知道,在最坏的情况下,需要多少时间。

如果打算用低成本的GPP 去完成实时信号处理的任务,执行时间的预测大概不会成为什么

问题,应为低成本GPP 具有相对直接的结构,比较容易预测执行时间。然而,大多数实时

DSP 应用所要求的处理能力是低成本GPP 所不能提供的。

这时候,DSP 对高性能GPP 的优势在于,即便是使用了高速缓存的DSP,哪些指令会放进

去也是由程序员(而不是处理器)来决定的,因此很容易判断指令是从高速缓存还是从存储

器中读取。DSP 一般不使用动态特性,如转移预测和推理执行等。因此,由一段给定的代

码来预测所要求的执行时间是完全直截了当的。从而使程序员得以确定芯片的性能限制。

7 定点DSP 指令集

定点DSP 指令集是按两个目标来设计的:

使处理器能够在每个指令周期内完成多个操作,从而提高每个指令周期的计算效率。

将存贮DSP 程序的存储器空间减到最小(由于存储器对整个系统的成本影响甚大,该问题

在对成本敏感的DSP 应用中尤为重要)。

为了实现这些目标,DSP 处理器的指令集通常都允许程序员在一个指令内说明若干个并行

的操作。例如,在一条指令包含了MAC 操作,即同时的一个或两个数据移动。在典型的例

子里,一条指令就包含了计算FIR 滤波器的一节所需要的所有操作。这种高效率付出的代

价是,其指令集既不直观,也不容易使用(与GPP 的指令集相比)。

GPP 的程序通常并不在意处理器的指令集是否容易使用,因为他们一般使用象C 或C++等

高级语言。而对于DSP 的程序员来说,不幸的是主要的DSP 应用程序都是用汇编语言写的

(至少部分是汇编语言优化的)。这里有两个理由:首先,大多数广泛使用的高级语言,例

如C,并不适合于描述典型的DSP 算法。其次,DSP 结构的复杂性,如多存储器空间、多

总线、不规则的指令集、高度专门化的硬件等,使得难于为其编写高效率的编译器。

即便用编译器将C 源代码编译成为DSP 的汇编代码,优化的任务仍然很重。典型的DSP 应

用都具有大量计算的要求,并有严格的开销限制,使得程序的优化必不可少(至少是对程序

的最关键部分)。因此,考虑选用DSP 的一个关键因素是,是否存在足够的能够较好地适应

DSP 处理器指令集的程序员。

8 开发工具的要求

因为DSP 应用要求高度优化的代码,大多数DSP 厂商都提供一些开发工具,以帮助程序员

完成其优化工作。例如,大多数厂商都提供处理器的仿真工具,以准确地仿真每个指令周期

内处理器的活动。无论对于确保实时操作还是代码的优化,这些都是很有用的工具。

GPP 厂商通常并不提供这样的工具,主要是因为GPP 程序员通常并不需要详细到这一层的

信息。GPP 缺乏精确到指令周期的仿真工具,是DSP 应用开发者所面临的的大问题:由于

几乎不可能预测高性能GPP 对于给定任务所需要的周期数,从而无法说明如何去改善代码

的性能。

- 【新要闻】晏殊的词集 三首小词请查收

- 世界快资讯:Android N更新哪些内容?Android N更新详情汇总

- 天天热议:正宗糖醋蒜的腌制方法 醋泡大蒜

- 全球快播:音悦台MV怎么下载?

- 每日时讯!魅族mx4好用吗?魅族MX4全面测评详细介绍

- 全球微速讯:iPhone锁屏密码忘了怎么办 苹果手机忘记锁屏密码两种解决方法

- 即时看!红米2增强版什么时候上市推出?红米2增强版多少钱?

- 环球热点!iOS测试UI的工具――Automation

- 世界消息!企鹅直播和斗鱼tv是什么关系?

- 天天快资讯:简单好吃早餐做法大全 最美味的早餐做法三则分享

- 【全球独家】矢志不移什么意思 矢志不移解释

- 世界消息!XP如何升级Win10_XP升级Win10教程

- 当前热议!iphone5 拆机图解教程

- 世界热头条丨iphone图标怎么更换 图解操作iPhone图标

- 每日视讯:支付宝蚂蚁庄园小鸡问答 猜一猜以下哪种水果的含糖量其实更高

- 今日关注:如何设置抖音透明头像?

- 【天天热闻】信号避雷器原理及特性介绍

- 世界信息:oppo r9s怎么连接电脑 oppo r9s正确连接电脑方法教程

- 天天短讯!小本投资项目推荐 中小投资项目

- 当前速递!iphonese2和iphone8哪个好?iphone8和iphonese2参数对比介绍

- 每日快看:iphone5c多少钱 苹果iphone5s价格多少

- 【环球速看料】华为p50和p50pro哪个好?华为p50对比p50pro的区别分析

- 今日热议:右键新建没有Word怎么办?

- 全球新资讯:小娘惹电视剧 全集45集剧情介绍

- 每日聚焦:一个电路教会你设计NPN三极管放大电路

- 环球新消息丨小米4C和小米4i哪个好 小米4C与4i的区别对比评测详解

- 今日热门!iPhone开机画面提示语去掉方法[图文]

- 微资讯!diy是什么意思-电脑diy组装教程

- 全球动态:佳域S3标准版和高配版哪个好?参数区别对比

- 全球播报:微信界面怎么设置皮肤

- 全球热议:技嘉主板常见问题与解答

- 今热点:如何安装AppSync补丁 两种完美方法安装AppSync补丁

- 长征七号A运载火箭成功发射中星1E卫星 实现连续三次发射成功

- 环球关注:国产加密手机为何这么火?国产加密手机火爆原因分析

- 天天热讯:qq群怎么匿名聊天

- 看热讯:OPPO FindX2和华为p40哪个好?为一块超感屏唱征服

- 热点评!如何使用百度网盘解析种子

- 魅族PANDAER发布白金星舟耳机与音箱新品 续航更长可降噪

- 环球快资讯:华为mate9什么时候出 华为mate9配置以及价格介绍

- 【环球聚看点】魅族X8和魅族16X哪个值得买 魅族16X和8X区别对比

- 提前激活iPhone14每台罚款20万:新机采用“灵动岛”挖孔设计

- 当前视讯!富士mini25怎么用 富士mini25使用技巧介绍

- 每日热点:小米红米1S手机做工怎么样 红米1S电信版拆机图评测

- 中国6最多、最顺利号码!15666666666靓号拍卖 已有10131次围观

- 【全球速看料】中国移动、联通、电信的4G套餐哪家最划算?

- 育碧公开舞力全开2023版游戏 XboxOne等版本预计11月上线

- Apple Watch Ultra电池容量揭晓:开启低功耗模式后可达到60小时

- 提前激活每台罚款20万!iPhone 14 Pro包装盒提前看:没有塑封包装

- 中国功夫游戏《师父》官宣11月9日登陆NS!直面会后开放预约

- Intel展示80Gbps的雷电新接口 每个通道40Gbps

- 三星全面推广SmartThings 并官宣旗下家电等保修期进一步延长

- 集邦咨询:预测三季度笔电面板出货将环减一成多 仅4510万片

- 东风风行S60EV已通过申报 前脸较前代有大幅变化设计更现代

- 摩托罗拉Edge30Ultra登陆印度市场 主摄为200MP规格支持快充

- 大立光披露最新财务数据:上月营收环增14% 增幅略高于预期

- 神舟十四号乘组在太空吃月饼度中秋:与月亮和嫦娥触手可及

- 大疆最新款运动相机将到来 磁吸拓展形式更加丰富拍摄更便捷

- 全球今热点:贝佐斯的火箭发射失败 但意外验证了逃逸系统

- 焦点速讯:前方高能!索尼SOP一次性展示10款大作

- 环球热门:iPhone14换电池贵了200!容量和13一样但是涨价

- 【世界时快讯】苹果:iOS不能回滚 但是安全补丁可以!

- 最新消息:全新3A大作!EA和光荣联合开发狩猎游戏

- 每日快报!更接近人类驾驶,特斯拉FSD来到临界点?

- 热点在线丨野炊2《塞尔达传说 王国之泪》正式定档,《双人成行》登陆NS

- 天天快资讯:仅需799元 智米纯净加湿器雨林上线众筹

- 环球看点!无感佩戴,耳机的难题它都解决了:索尼开放式真无线耳机LinkBuds

- 环球看热讯:英特尔院士Tom Petersen:持续耕耘游戏优化 确保优质用户体验

- 每日看点!OPPO Watch 3 Pro体验报告:以旗舰特性,开启腕上智慧生活

- 每日快看:豪威推出用于笔记本电脑的HDR 4K摄像头模块OV08X

- 每日关注!苹果iOS 16系统正式版发布:有锁屏个性化和自定义等功能

- 【速看料】抖音921好物节氛围正浓!品牌商家达人乘势增长喜迎开门红

- 今日讯!以电力成就算力 施耐德电气以数字配电方案助力华云数据湖电力运维高效进阶

- 环球快看点丨开辟清洁能源新赛道四季沐歌勇扛“空气源热泵”大旗

- 【当前热闻】超宽、融合、智能、开放,新华三提出云智原生数据中心网络建设思路

- 热议:倍思Ga5Pro氮化镓多功能桌面快充充电器:充电和接口扩展一个搞掂

- 当前报道:宝妈宝爸该用什么枕头?米家智能枕体验,支持睡眠分析与智能联动

- 世界今热点:苹果98元挂绳卖断货/贝佐斯火箭发射失败/新手爸爸大脑会“萎缩”

- 环球新资讯:3DEXPERIENCE线上云平台支持离线工作?是真的!

- 环球精选!对标Redmi!realme Watch 3 Pro发布

- 苹果新机完成3C认证 信息显示其可支持29W快充并兼容多个协议

- iPhone14系列部分订单已显示准备发货 原定发售日为本周五

- 华硕PN52迷你主机全新亮相 16GB内存成标配 售价最高超五千

- 最新款高端苹果手机4K ProRes确定所需存储空间:至少256G

- YOGAPro14s新BIOS接受官方测试:处理器大小核可自定义调整

- 报道称谷歌将为高端ChromeOS产品添加更多更优质的视频效果

- 全球聚焦:在考虑入手三星Fold4的朋友,来看看我的真实用机感受

- 【聚看点】三维菁彩声 为央视秋晚增添8K视听科技亮点

- 全球热文:【新机】又一款套娃机发布,5000mAh+67W快充

- 环球快看:一台12999元的折叠屏手机,买它的人到底有多大的底气?

- 动画电影机器人总动员将发布4K超清蓝光碟 封面将获得特别设计

- 苹果14Pro/Max版本将支持双频GPS定位 所在位置可更加精确

- 【世界播资讯】iPhone11怎么连接电脑?iPhone11信任并连接电脑图文教程

- 焦点关注:飞机上拍到神仙?网友拍到云上站着人,还自带佛光

- 环球关注:iPhone 14系列新机真的香,搭配闪魔配件使用更佳

- 全球热推荐:为什么这么薄?拆解欣博阅G6

- 世界观察:华为nova3i怎么样 华为Nova3i配置参数、价格及真机图赏

- 当前看点!超链接去掉下划线方法

- 每日短讯:荣耀4C有几个版本?华为荣耀4C畅玩版各版本区别介绍

- 每日快播:夏天防晒科普:SPF指数是什么? 防晒霜防晒指数

- 电子纸厂商元太八月营收约环增一成多 同增翻倍再创单月新高

新闻排行

精彩推荐

- 【世界时快讯】苹果:iOS不能回滚 但是安全补丁可以!

- 焦点速讯:前方高能!索尼SOP一次性展示10款大作

- 最新消息:全新3A大作!EA和光荣联合开发狩猎游戏

- 全球今热点:贝佐斯的火箭发射失败 但意外验证了逃逸系统

- 环球热门:iPhone14换电池贵了200!容量和13一样但是涨价

- 热点在线丨野炊2《塞尔达传说 王国之泪》正式定档,《双人成行》登陆NS

- 天天快资讯:仅需799元 智米纯净加湿器雨林上线众筹

- 【当前热闻】超宽、融合、智能、开放,新华三提出云智原生数据中心网络建设思路

- 热议:倍思Ga5Pro氮化镓多功能桌面快充充电器:充电和接口扩展一个搞掂

- 今日讯!以电力成就算力 施耐德电气以数字配电方案助力华云数据湖电力运维高效进阶

超前放送

- 即时:一种手机准确测量环境温度...

- 【世界播资讯】2017中国智能手机...

- 天天百事通!最美晚安心语唯美的...

- 焦点速递!HTC U11和三星S8哪个...

- 【世界时快讯】TPOS超薄外置光驱拆解

- 全球热文:初学者买什么吉他 具...

- 天天快看:三星手机移动数据连接...

- 今日讯!2020国内奶粉排名前十名...

- 最资讯丨风暴播放器调出播放进度...

- 世界观焦点:小年夜是指哪一天几...

- 每日头条!蚂蚁庄园6月20日答案最...

- 世界看点:iphone怎么添加厦门公...

- 天天即时看!好看的韩国爱情喜剧...

- 全球观点:一差半错是什么意思 ...

- 天天简讯:电视液晶屏哪个品牌最...

- 环球动态:鬼谷子下山的故事 鬼...

- 世界讯息:支付宝扫福字2022什么...

- 全球即时:Corel VideoStudio ...

- 天天视讯!特朗普美国正迅速成为...

- 天天信息:icloud存储满了怎么办...

- 天天快报!怎样水养富贵竹 水养...

- 【独家焦点】千元以下智能手机有...

- 要闻:在ADSP-BF561上实现与优化的H.264

- 新消息丨ota是什么?ota升级是什...

- 全球观热点:fps不稳定怎么办

- 热点评!螺杆空压机工作原理是什...

- 全球最资讯丨手写电脑多少钱 手...

- 【播资讯】三星W2016手机怎么样...

- 世界快资讯:acer笔记本电脑怎么样

- 环球时讯:轩辕传奇手游攻略 轩...

- 环球新消息丨先科热水器怎么样 ...

- 世界新资讯:安卓手机视频格式有...

- 世界速看:mds文件用什么打开

- 环球视讯!为什么中国IC市场越来...

- 天天微速讯:怎样进入dos?进入d...

- 焦点播报:空调一小时几度电

- 当前时讯:傍组词语 汉字傍组词语

- 当前视点!科威特70度等于中国多...

- 环球视讯!iPhoneSE2屏幕分辨率是多少?

- 环球微动态丨梨花烫最新款短发 ...

- 【天天快播报】LCD液晶电视各接...

- 当前关注:10万元左右的车哪款好...

- 全球热门:ireader(爱读掌阅)安卓...

- 世界焦点!红魔3手机值不值得买...

- 当前快报:大漠孤火烟直长河落日...

- 玉兔二号月球车已登陆月背工作三...

- 天天新动态:一加9和一加9pro区...

- 世界快讯:清平乐·金风细细——...

- 天天时讯:iPhone12系列电池容量...

- 环球速看:windows bat(批处理):IF详解